What to Know about 3D NAND, The Future of Flash Memory

Odds are pretty high that you’ve spent little to no time thinking about 3D NAND technology, but your customers have and here’s why: Data.

All the hottest concepts in technology — the cloud, big data, internet of things, etc. — require storing, processing and sharing data, and those data requirements are increasing every day.

Traditional 2D NAND-based flash memory has been a workhorse of our digital storage economy, but its architecture has reached its physical limits, so suppliers are moving on to the next generation: 3D NAND.

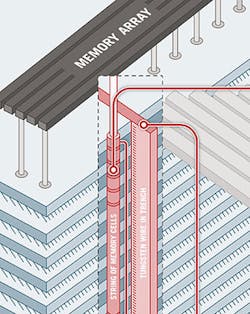

As the name suggests, 3D NAND consists of tiers of memory capacity stacked on top of each other (see graphic below). This new architecture delivers significantly more storage capacity at a lower cost per gigabyte, making the transition to 3D NAND a no brainer.

Unfortunately, as with most new technologies, the devil is in the details. Currently, manufacturing 3D NAND at scale is a challenge given all the new processes steps required to stack and connect each tier. Even so, the industry is making great strides and many analysts believe 2018 is the year 3D NAND goes mainstream.

Why Now?

Samsung, Toshiba and INTEL/Micron were the leaders to high-volume manufacturing (HMV) of 3D NAND from 2013, but costs remained high due to production complexities. Progress has been made in the five years since, but rising demand coupled with a potential shortage of 2D NAND supply has created a perfect storm opportunity for the entire industry — chipmakers, equipment manufacturers, materials suppliers — to work together to solve these last mile challenges.

What’s It Going to Take?

The transition from 2D to 3D NAND architecture required significant changes to the way new memory devices are manufactured, but the good news is that the technical challenges are being overcome. In 2D the challenge was to shrink laterally, whereas in 3D the challenges are driven mainly by the processes of etching and deposition at extreme aspect ratios (ratio of a hole diameter with its depth). As with other new technologies, a focus on process efficiency, materials innovations, and contamination controls will be crucial to achieving High Volume Manufacturing (HVM) that meets performance, yield, and cost requirements.

In particular, for 3D NAND to reach maturity, these challenges need to be addressed:

- Etch & Deposition: Creating complex 3D structures with very high-aspect-ration (HAR) features is complicated and requires extreme precision and, ultimately, process uniformity and repeatability to achieve scale. To help visualize this challenge, the world’s tallest building— the Burj Khalifa in Dubai — is 828 m high with a base of 140 m. That’s an aspect ratio (AR) of about 6 to 1. 3D NAND structures already work at an AR of around 60 to 1 and this will continue to increase in coming years. Moreover, as multi-layered stack heights increase, so does the difficulty in achieving consistent etch and deposition results at the top and the bottom of the memory array.

One example of an Etch challenge is the hard mask material typically used for HAR etching. It’s typically amorphous carbon, and its job is to protect patterned areas of material while allowing features to be exposed to Plasma Etching based material removal, but it’s reaching the limit as it is not plasma-resistant enough to do this job as aspect ratios increase. Some of the possible solutions to this challenge will require innovative new materials and development measures to bring higher resistance, stability, repeatability, and optimization to critical etch processes. - The Slowdown: As the stack gets taller, the silicon channels extends longer, and the speed of the device becomes limited by the mobility of electrons travelling through the channels. Germanium doping (currently in development) is one known method for improving electron mobility, and suppliers are working to find even more efficient means of providing germanium dopants for 3D NAND.

To address conductivity issues as the stack increases in height, it may be necessary to apply alternative metals to tungsten, which is the current standard. Chemical elements such as cobalt, ruthenium, or molybdenum have lower resistivity and better reliability at thin dimensions and could become essential to maintaining overall device performance. - Contamination Control: As the number of memory cells increase in a 3D stack, a defect in a single cell could affect the performance of the entire cell string and hence the device. As a result, all potential contamination areas must be identified and proper steps taken to avoid any and all imperfections. Those steps range from raw materials, to synthesis of chemistries, handling of chemistries, and finally dispensing to the wafer.

For example, the presence of particulates in one cell can effectively kill an entire cell string. Also, metallic contamination (e.g. Fe, Cr, etc. from stainless steel) can destroy the cell electrical properties if they find their way to the cell layers. Likewise, large quantities of plasma etch byproducts from billions of HAR channel holes can adsorb into wafer carrier equipment and later evolve causing defects on the wafer structure. Innovations in wafer carriers (FOUPs) are required to counteract this effect. Lastly, photosensitive masking material (Photoresist), which is required at high viscosity to pattern such HAR features, is prone to bubble formation that leads to patterning defects. Innovations in pumping/filtration and dispensing are made to avoid such bubble formation.

Every generation of 3D NAND is becoming more sensitive to contamination, as with shrinking geometries in general, so material purity is critical. Without adequate filtration and purification, process requirements that enable increased layers and dimension shrinkage for advanced chip development cannot be achieved.

Mark Puttock is a director at Entegris, specializing in Advanced Deposition, Speciality Materials and Plating

About the Author

Mark Puttock

Director Advanced Deposition and Plating, Strategic Technology Account Management

Mark Puttockis the Director Advanced Deposition and Plating, Strategic Technology Account Management for Entegris, which provides a clean chemical delivery environment with contamination-controlled chemical packaging, filtration, pumps, and fluid handling products that will increase product yield and reduce financial loss.